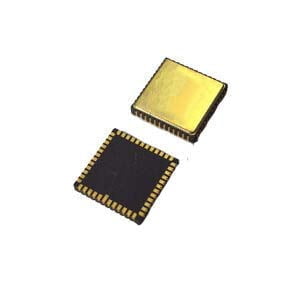

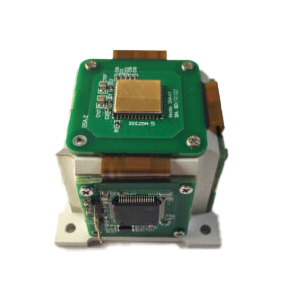

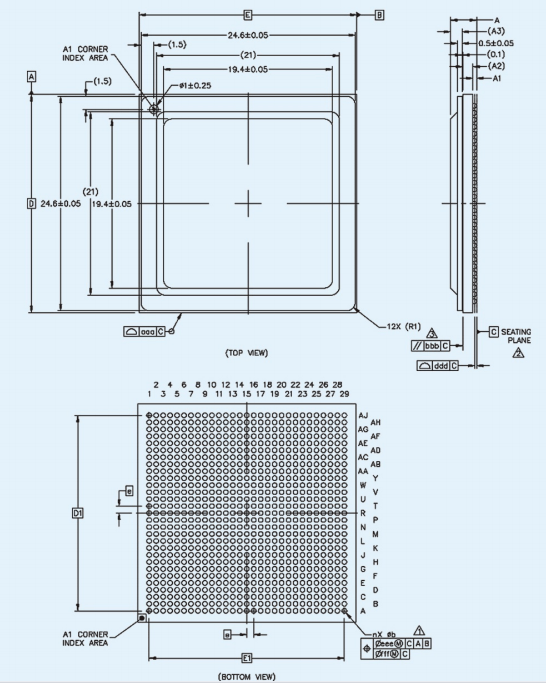

Military-grade Digital Signal Processor

Introduction

ER-DSPC-20B processor is a 32-bit floating-point military-grade digital signal processor with an independent architecture design. It was launched in the first half of 2020. This processor is mainly designed for applications with demanding environments, such as missile-borne, airborne radar countermeasures, and SAR imaging.

Technical Characteristics:

Based on the independent architecture EC104E core;

SIMD+VLIW architecture;

Meet military temperature requirements;

Typical Technical Indicators

DSP Frequency: 500MHz

Computing Performance: 42GFLOPS

On-chip Storage: 48Mbit

Communication Bandwidth: 100Gbps

Typical Power Consumption: 3.5W

Interface List

| IO Type | Performance Parameter | |

| DDR | Particle Type | DDR3/4 |

| External Data Width | 72bit (including ECC) | |

| Number of Controllers | 1 | |

| Maximum Total Bandwidth | 204.8Gbp | |

| RapidIO | Support Protocol Version | 2.2 |

| Number of LANE | 4 | |

| Number of Controllers | 4 | |

| Maximum Total Bandwidth | 100 Gbps | |

| HX-Link

(Custom protocol) |

Support Protocol Version | 1.0 |

| Number of LANE | 4 | |

| Number of Controllers | 1 | |

| Maximum Total Bandwidth | 20 Gbps | |

| JESD204B

(The controller which reuse HX-Link) |

Support Protocol Version | JESD 204B |

| Number of LANE | 4 | |

| Number of Controllers | 1(AD/DA) | |

| Maximum Total Bandwidth | 32 Gbps | |

| Ethernet | / | 10/100/1000MHz Ethernet,S/RGMII |

| Parallel Port(EMIF) | / | 1 bit chip select, 26bit address, 16bit data |

| GPIO | / | 80 bit |

| UART/I2C/SPI | Support | |

Application Techniques

1.What is the Device Interface Definition of MEMS North Seeker

2.What Performance is the FOG sensor in FOG North Finder

3.Where are MEMS Gyroscopes Used?

4.Research Background and Current Status of MEMS IMU

5.How do parameters affect the performance of the quartz accelerometer?

6.Background and Development Status of MEMS Inertial Sensors

More Products