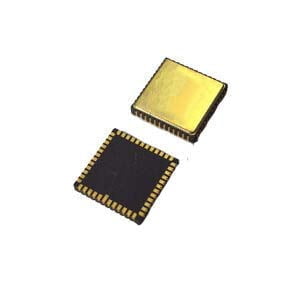

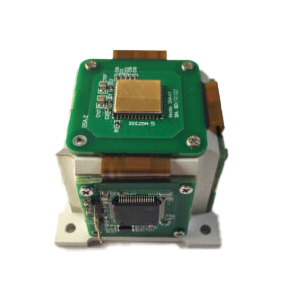

High Efficiency Cloud CPU

Introduction

ER-CPU-35C is a general processor of Ericco for the server field. It integrates 16 high-performance processor cores on chip and adopts the new Arch™, based on the compatible ER-CPU-35CL motherboard design, optimizes the packaging form to maintain system and application software compatibility.

Main Features

New instruction system: Optimized instruction efficiency based on Arch™

High-end multiplexing: Support up to 16 channels, 256 core interconnect architecture, overall CC-NUMA

High system performance: Unixbench scores over 9000

Efficient virtualization: KVM virtul machine computing efficiency is more than 95%

High Speed interconnection: Multi-level Cache consistency protocol for efficient local and cross-chip access

High memory bandwidth: Flexible configuration of memory channels provides ample bandwidth

Expanded I/O support: Equipped with a new-generation bridge, greatly increasing the effective PCIE bandwidth

Parameters

| Master frequency | 2.0GHz-2.2GHz |

| Peak operation speed | 560GFlops@2.2GHz |

| Core number | 16 |

| Processor core | 64-bit superscalar processor core;

Support for Arch™ instruction system; Support 128/256-bit vector instruction; Four launch out of order execution; 4 fixed point units, 2 vector units and 2 access storage units |

| High-speed Cache | Each processor core contains a 64KB private level-1 instruction cache and 64KB private level-1 data cache;

Each processor core contains 256KB private level-2 cache; All processor cores share 32MB level-3 cache |

| Memory controller | 4 72-bit DDR4-3200 controllers;

Support ECC verification |

| High speed I/O | 1 HyperTransport 3.0 IO interface (HT0);

3 high speed interfaces with consistent interconnection (HT1, HT2, HT3) |

| Other I/ O | 1 SPI, 1 UART, 3 I2C, 16 GPIO interfaces |

| Power consumption management | Support the main module clock dynamic shutdown;

Support the main clock domain dynamic frequency conversion; Supports dynamic voltage regulation in the main voltage domain. |

| Typical power consumption | 130W@2.2GHz |

Application Techniques

1.What is the Device Interface Definition of MEMS North Seeker

2.What Performance is the FOG sensor in FOG North Finder

3.Where are MEMS Gyroscopes Used?

4.Research Background and Current Status of MEMS IMU

5.How do parameters affect the performance of the quartz accelerometer?

6.Background and Development Status of MEMS Inertial Sensors

More Products